# with Output Disconnect

#### **■** INTRODUCTION:

The CE8425 devices provide a power supply solution for products powered by either a one-cell Li-lon or Li-polymer, or a two to three-cell alkaline, NiCd or NiMH battery. The converter generates a stable output voltage that is adjusted by an external resistor divider. It provides high efficient power conversion and is capable of delivering output currents up to 1.5A at 5V at a supply voltage down to 2V.

The implemented boost converter is based on a fixed switching frequency (500kHz typical), current-mode controller using a synchronous rectifier to obtain maximum efficiency. Boost switch and rectifier switch are connected internally to provide the lowest leakage inductance and best EMI behavior possible. The current-mode control scheme provides fast transient response and good output voltage accuracy. At light load, the converter will automatically enter into Pulse Frequency Modulation (PFM) operation to reduce the dominant switching losses. During PFM operation, the IC consumes very low quiescent current and maintains high efficiency over a wide load current range.

The converter can be disabled to minimize battery drain. During shutdown, the load is completely disconnected from the battery.

The device allows use of small inductors and output capacitors for USB devices.

#### FEATURES:

- 97% Efficiency at V<sub>OUT</sub>=5V from 3.3V Input

- Device Quiescent Current: 37µA (Typ)

- Guaranteed 2.5A Output Current at V<sub>OUT</sub>=5V from 3.3V Input

- 500kHz PWM Switching Frequency

- Synchronous and Embedded Power MOSFETs, No Schottky Diode Required

- Low R<sub>DS(ON)</sub> (main switch/synchronous switch) at 5.0V output: 20/40mohm

- Input Voltage Range: 1.8V to 5.25V

- Adjustable Output Voltage Range: from 2.5V to 5.5V

- Pulse Frequency Modulation Operation for Improved Efficiency at Low Output Power

- Current Mode Operation with Internal Compensation for Excellent Line and Load Transient Response

- Logic Controlled Shutdown(<1µA)</li>

- Load Disconnect During Shutdown

- Automatic output discharge at shutdown: CE8425A: Auto output discharge function CE8425B: No output discharge function

- Low Battery Comparator

- Internal Soft-Start to Limit Inrush Current

- Over Current Protection

- Input Under Voltage Lockout

- Output Over Voltage Protection

- Over-Temperature Protection

- Available in 2.1mm x 2.1mm QFN10 Package

#### **■** APPLICATIONS:

- All Single Cell Li or Dual Cell Battery Operated Products as Tablet PC, Smartbook and Other Portable Equipment

- Products including portable HDMI and USB-OTG

- USB Hosts Without Native 5V Supplies

- USB Charging Port (5V)

- Power Bank, Battery Backup Units

- Wireless Peripherals

- Portable Audio Plavers

- Personal Medical Devices

- Industrial Metering Equipments

- DC/DC Micro Modules

# ORDER INFORMATION

| Device No.  | Output Voltage | Package       | Packaging           |  |

|-------------|----------------|---------------|---------------------|--|

| CE8425AQD10 | Adjustable     | QFN2.1x2.1-10 | 3000 parts per reel |  |

| CE8425BQD10 | Adjustable     | QFN2.1x2.1-10 | 3000 parts per reel |  |

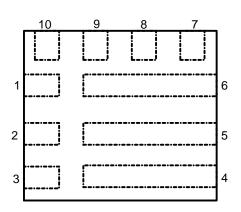

# **■ PIN CONFIGURATION:**

# **Top View**

(QFN2.1X2.1-10)

| PIN |                 | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----|-----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME            | IIPE                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 1   | CE              | ı                   | Chip Enable Input. Internal integrated with 1Mohm pull down resistor.  CE=High: Normal free running operation.  CE=Low: Shutdown; quiescent current <1µA. Output capacitor can be completely discharged through the load or feedback resistors.  If CE is undefined, pin SW may ring.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2   | LBI             | I                   | Low Battery Comparator Input (comparator enabled with CE).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 3   | V <sub>IN</sub> | I                   | Battery Supply Input Voltage. The device gets its start-up bias from $V_{IN}$ . Once $AV_{OUT}$ exceeds 2.3V, bias comes from $AV_{OUT}$ . Thus, once started, operation is completely independent from $V_{IN}$ . Operation is only limited by the output power level and the battery's internal series resistance. The $V_{IN}$ pin should be connected to the positive terminal of the battery and bypassed with a low ESR ceramic bypass capacitor. Care should be taken to minimize the loop area formed by the bypass capacitor connections, the $V_{IN}$ pin, and the CE8425 AGND pin. The minimum recommended bypass capacitance is $1\mu F$ ceramic with a X5R or X7R dielectric and the optimum placement is closest to the $V_{IN}$ pin and the AGND pin. PCB trace length from $V_{IN}$ to the input filter capacitor(s) should be as short and wide as possible. |  |

|   | 1                 |     | <u> </u>                                                                                                                                                                                                      |

|---|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                   |     | Power Ground. Ground connection for high-current power converter node. High current return for the low-side driver and power main switch N-MOSFET. Connect PGND with large copper areas directly to the input |

| 4 | PGND              | Р   | and output supply returns and negative terminals of the input and output                                                                                                                                      |

|   |                   |     | filter capacitor(s).                                                                                                                                                                                          |

|   |                   |     | Tie this pin to the ground island/plane through the lowest impedance                                                                                                                                          |

|   |                   |     | connection available.                                                                                                                                                                                         |

|   |                   |     | Connect this pin to AGND.                                                                                                                                                                                     |

|   |                   |     | Boost and Rectifying Switch Input. Connect an inductor between this                                                                                                                                           |

| _ | 0)4/              |     | pin and V <sub>IN</sub> . Keep the PCB trace lengths as short and wide as is practical                                                                                                                        |

| 5 | SW                | ı   | to reduce EMI and voltage overshoot. If the inductor current falls to zero,                                                                                                                                   |

|   |                   |     | or pin CE is low, an internal anti-ringing switch is connected from this pin                                                                                                                                  |

|   |                   |     | to V <sub>IN</sub> to minimize EMI.                                                                                                                                                                           |

|   |                   |     | DC-DC Power Output (Drain of the Internal Synchronous Rectifier                                                                                                                                               |

|   |                   |     | P-MOSFET). PCB trace length from PV <sub>OUT</sub> to the output filter capacitor(s)                                                                                                                          |

|   |                   |     | should be as short and wide as possible. Care should be taken to                                                                                                                                              |

|   | 5.4               | 0   | minimize the loop area formed by the output filter capacitor(s)                                                                                                                                               |

| 6 | PV <sub>OUT</sub> |     | connections, the PV <sub>OUT</sub> pin, and the CE8425 PGND pin. The minimum                                                                                                                                  |

|   |                   |     | recommended output filter capacitance is 22µF ceramic with a X5R or                                                                                                                                           |

|   |                   |     | X7R dielectric and the optimum placement is closest to the PV <sub>OUT</sub> pin and                                                                                                                          |

|   |                   |     | the PGND pin. PV <sub>OUT</sub> is completely disconnected from V <sub>IN</sub> when CE is low,                                                                                                               |

|   |                   |     | due to the output disconnect feature.                                                                                                                                                                         |

|   |                   |     | IC Supply Voltage and Output Voltage Sense Input. Bias is derived                                                                                                                                             |

|   |                   |     | from AV <sub>OUT</sub> when AV <sub>OUT</sub> exceeds 2.3V. The AV <sub>OUT</sub> pin should be                                                                                                               |

|   |                   |     | connected to the DC-DC power output pin, PV <sub>OUT</sub> , and bypassed with a                                                                                                                              |

|   |                   |     | low ESR ceramic bypass capacitor for noise immunity consideration. Care                                                                                                                                       |

|   |                   |     | should be taken to minimize the loop area formed by the bypass capacitor                                                                                                                                      |

| 7 | AV <sub>OUT</sub> | I   | connections, the AV <sub>OUT</sub> pin, and the CE8425 AGND pin. The minimum                                                                                                                                  |

|   | 001               |     | recommended bypass capacitance is 1µF ceramic with a X5R or X7R                                                                                                                                               |

|   |                   |     | dielectric and the optimum placement is closest to the AV <sub>OUT</sub> pin and the                                                                                                                          |

|   |                   |     | AGND pin.                                                                                                                                                                                                     |

|   |                   |     | PCB trace length from AV <sub>OUT</sub> to the output filter capacitor(s) should be as                                                                                                                        |

|   |                   |     | short and wide as possible. AV <sub>OUT</sub> is also completely disconnected from                                                                                                                            |

|   |                   |     | V <sub>IN</sub> when CE is low, due to the output disconnect feature.                                                                                                                                         |

|   |                   | 3 I | Feedback Input.                                                                                                                                                                                               |

|   | FB                |     | Feedback Input to the gm Error Amplifier. Connect resistor divider tap to                                                                                                                                     |

|   |                   |     | this pin.                                                                                                                                                                                                     |

| 8 |                   |     | The output voltage can be adjusted from 2.5V to 5.5V by:                                                                                                                                                      |

|   |                   |     | $V_{OUT} = 1.2V \cdot [1 + (R1/R2)]$                                                                                                                                                                          |

|   |                   |     | The feedback networks should be connected directly to a dedicated                                                                                                                                             |

|   |                   |     | analog ground plane and this ground plane must connect to the AGND                                                                                                                                            |

|   |                   |     | pin. If no analog ground plane is available, then the ground connection of                                                                                                                                    |

| 10 | LBO  | 0 | Low Battery Comparator Output (open drain).                                 |

|----|------|---|-----------------------------------------------------------------------------|

|    |      |   | Connect this pin to PGND.                                                   |

|    |      |   | Return for output voltage set resistor divider.                             |

| 9  | AGND | I | not be in the path of large currents.                                       |

|    |      |   | signals. Provide a clean ground for the analog control circuitry and should |

|    |      |   | Analog Ground. The analog ground ties to all of the noise sensitive         |

|    |      |   | the system.                                                                 |

|    |      |   | PCB layout to minimize copper trace connections that can inject noise into  |

|    |      |   | Please keep FB away from the inductor and SW switching node on the          |

|    |      |   | area at FB pin should be small.                                             |

|    |      |   | directly as closely as possible. And FB is a sensitive signal node, trace   |

|    |      |   | The feedback network, resistors R1 and R2 must be connected to FB pin       |

|    |      |   | performance.                                                                |

|    |      |   | network to the PGND can inject noise into the system and effect             |

|    |      |   | the feedback network must tie directly to the AGND pin. Connecting the      |

<sup>(1)</sup> I = input; O = output; P = power

## ■ ABSOLUTE MAXIMUM RATINGS(1)

| PAR                              | AMETER                         | SYMBOL              | RATINGS               | UNITS |

|----------------------------------|--------------------------------|---------------------|-----------------------|-------|

| CE \                             | /oltage <sup>(2)</sup>         | V <sub>CE</sub>     | V <sub>OUT</sub> +0.3 | V     |

| Other Pi                         | ns Voltage <sup>(2)</sup>      |                     | 6                     | V     |

| Power Dissipation <sup>(3)</sup> | I OFN2 1X2 1-10                |                     | 2.5                   | W     |

| Package The                      | rmal Resistance <sup>(4)</sup> | $	heta_{ m JA}$     | 50                    | °C/W  |

| T ackage The                     | mai Nesistance                 | $	heta_{ m JC}$     | 10                    | °C/W  |

| Operating Junctio                | n Temperature Range            | T <sub>j</sub> 150  |                       | °C    |

| Lead Temperature(S               | Soldering, 10 sec)             | T <sub>solder</sub> | 260                   | °C    |

| Storage Tem                      | perature Range                 | T <sub>stg</sub>    | -65~150               | °C    |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

- (2) All voltages are with respect to network ground terminal.

- (3) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = [ $T_J$ (MAX)- $T_A$ ]/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- (4)  $\theta_{JA}$  is measured in the natural convection at  $T_A$ =25  $^{\circ}$ C on a four-layer Chipower Evaluation Board

# ■ RECOMMENDED OPERATING CONDITIONS(5)

|                                                         | MIN | NOM | MAX                   | UNITS |

|---------------------------------------------------------|-----|-----|-----------------------|-------|

| Supply voltage at V <sub>IN</sub>                       | 1.8 |     | 5.25                  | V     |

| Output voltage at PV <sub>OUT</sub> , AV <sub>OUT</sub> | 2.5 |     | 5.5                   | V     |

| CE                                                      | 0   |     | V <sub>OUT</sub> +0.3 | V     |

| All other pins                                          | 0   |     | 5.5                   | V     |

| Operating Ambient temperature range, T <sub>A</sub>     | -40 |     | 85                    | °C    |

| Operating junction temperature range, T <sub>j</sub>    | -40 |     | 125                   | °C    |

<sup>(5)</sup> The device is not guaranteed to function outside its operating conditions.

### **■ ELECTRICAL CHARACTERISTICS**

(V<sub>CE</sub>=V<sub>IN</sub>=2.4V, V<sub>OUT</sub>=5V, I<sub>OUT</sub>=500mA, T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                                  |                            | SYMBOL                                             | CONDITIO                                                                                                   | ONS     | MIN   | TYP <sup>(6)</sup> | MAX   | UNITS |

|--------------------------------------------|----------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------|-------|--------------------|-------|-------|

| Input V <sub>IN</sub> UVLO Threshold       |                            | $V_{UVLO}$                                         | V <sub>IN</sub> Rising                                                                                     |         |       |                    | 1.78  | V     |

| V <sub>IN</sub> UVLO Hysteresis            |                            | V <sub>UVLO_HYS</sub>                              |                                                                                                            |         |       | 0.1                |       | V     |

|                                            | V <sub>IN</sub>            |                                                    | $V_{CE}=V_{IN}=1.8V$ , $V_{OUT}=5V$ , no load, Measured on $V_{IN}$ pin                                    |         |       | 10                 |       | μA    |

| Quiescent Current                          | V <sub>OUT</sub>           | - I <sub>Q</sub>                                   | V <sub>CE</sub> =V <sub>IN</sub> =1.8V, V <sub>OUT</sub> =5V, no load,<br>Measured on V <sub>OUT</sub> pin |         |       | 27                 |       | μΑ    |

| Shutdown Current                           |                            | I <sub>SHDN</sub>                                  | V <sub>CE</sub> =0V, V <sub>IN</sub>                                                                       | =2.4V   |       | 0.1                | 1     | μA    |

| CE High-Level Thresh                       | nold                       | $V_{CEH}$                                          | CE Risi                                                                                                    | ng      | 1.2   |                    |       | V     |

| CE Low-Level Thresh                        | old                        | $V_{CEL}$                                          | CE Falli                                                                                                   | ng      |       |                    | 0.3   | V     |

| Soft-start time                            |                            | T <sub>SS</sub>                                    |                                                                                                            |         |       | 1                  |       | ms    |

|                                            |                            |                                                    | V <4V                                                                                                      | CE8425A |       | 0.75               |       | Α     |

| Linear Charge Curren                       |                            |                                                    | V <sub>OUT</sub> ≤1V                                                                                       | CE8425B |       | 1.3                |       | Α     |

| Linear Charge Curren                       | ( LIIIIII.                 | CHARGE                                             | 4)/ )/ 000/)/                                                                                              | CE8425A |       | 0.7                |       | Α     |

|                                            |                            | 1V <v<sub>OUT&lt;90%V<sub>IN</sub> CE8425E</v<sub> | CE8425B                                                                                                    |         | 1.2   |                    | Α     |       |

| Output Discharge Resistor                  |                            | R <sub>DSC</sub>                                   | For CE8425A only                                                                                           |         |       | 100                |       | Ω     |

| Low Side Main N-FET                        | R <sub>ON</sub>            | R <sub>NDS(ON)</sub>                               | V <sub>OUT</sub> =5V                                                                                       |         |       | 20                 |       | mΩ    |

| Synchronous P-FET F                        | R <sub>ON</sub>            | R <sub>PDS(ON)</sub>                               | V <sub>OUT</sub> =5V                                                                                       |         |       | 40                 |       | mΩ    |

| Switching Frequency                        |                            | F <sub>SW</sub>                                    |                                                                                                            |         |       | 500                |       | KHz   |

| Maximum Duty Cycle                         |                            | D <sub>MAX</sub>                                   |                                                                                                            |         | 90    | 95                 |       | %     |

| Main N-FET Current L                       | _imit <sup>(7) (8)</sup>   | I <sub>LIM1</sub>                                  |                                                                                                            |         | 5.0   | 6.5                |       | Α     |

| Feedback Reference                         | Feedback Reference Voltage |                                                    |                                                                                                            |         | 1.182 | 1.2                | 1.218 | V     |

| Output Over Voltage Protection             |                            | V <sub>OVP</sub>                                   |                                                                                                            |         |       | 5.8                |       | V     |

| LBI Voltage Threshold                      |                            | $V_{LBI}$                                          | V <sub>IN</sub> Falling                                                                                    |         | 1.176 | 1.2                | 1.224 | V     |

| LBI Input Hysteresis                       |                            | V <sub>LBI_HYS</sub>                               |                                                                                                            |         |       | 20                 |       | mV    |

| Thermal Shutdown <sup>(7)</sup>            |                            | T <sub>SD</sub>                                    |                                                                                                            |         |       | 150                |       | °C    |

| Thermal Shutdown Hysteresis <sup>(7)</sup> |                            | T <sub>HYS</sub>                                   |                                                                                                            |         |       | 20                 |       | °C    |

<sup>(6)</sup> Typical numbers are at 25°C and represent the most likely norm.

<sup>(7)</sup> Specification is guaranteed by characterization and not 100% tested in production.

<sup>(8)</sup> Duty cycle affects current limit due to ramp generator.

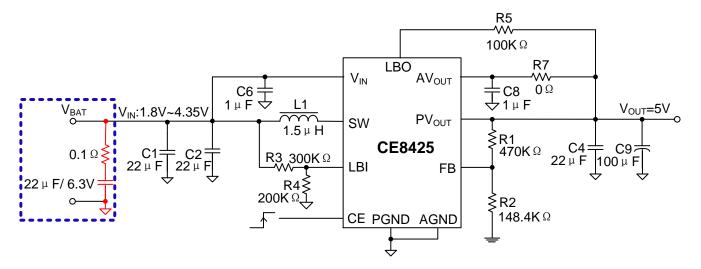

# **■ TYPICAL APPLICATION CIRCUIT**

**Figure 1 Standard Application Circuit**

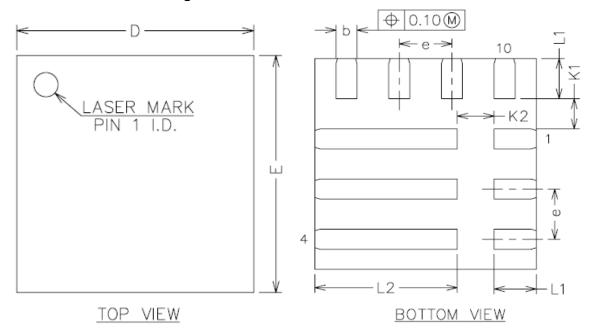

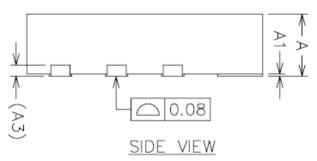

## PACKAGING INFORMATION

# • QFN2.1X2.1-10 Package Outline Dimensions

COMMON DIMENSIONS

(UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN     | NOM  | MAX  |  |  |

|--------|---------|------|------|--|--|

| Α      | 0.50    | _    | 0.65 |  |  |

| A1     | 0.00    | 0.02 | 0.05 |  |  |

| А3     | 0.10REF |      |      |  |  |

| Ь      | 0.15    | 0.20 | 0.25 |  |  |

| D      | 2.00    | 2.10 | 2.20 |  |  |

| E      | 2.00    | 2.10 | 2.20 |  |  |

| е      | 0.40    | 0.50 | 0.60 |  |  |

| K1     | 0.20    | 0.30 | 0.40 |  |  |

| K2     | 0.25    | 0.35 | 0.45 |  |  |

| L1     | 0.35    | 0.40 | 0.45 |  |  |

| L2     | 1.30    | 1.35 | 1.40 |  |  |

NOTES:

ALL DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSION.

### © Nanjing Chipower Electronics Inc.

Chipower cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Chipower product. No circuit patent license, copyrights or other intellectual property rights are implied. Chipower reserves the right to make changes to their products or specifications without notice. Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete.